雙面布局貼補強,FPC焊接很受傷

發布時間:2024-03-11 17:15

高速先生成員--王輝東

FPC上有器件的位置添加補強,按理說是合情合理,為什么加了補強,就無法焊接。請走進今天的案例,為你揭秘,看看你是否也有相似的經歷。

生活就像巧克力,你永遠不知道下一顆是什么味道。

一大早,林如煙和趙理工剛來到辦公室、大師兄讓他們稍微整理下,就開始講FPC補強的介紹、分類、作用,特別是關于補強的案例,真的讓他們感慨事后諸葛亮,事前很迷茫。

什么是補強

補強板,顧名思義作用在于給FPC補強,為的是能夠順利在FPC上面貼裝元器件,補強板有維持FPC外形穩定性的作用;

軟板在具有輕型、薄型、柔性的同時,也失去了剛性的性能,那么為了使產品指定部位增加一定的厚度和剛性,以便于客戶的后續安裝或裝配,我們就需要在這些位置貼上一塊剛性的板材,即補強板。

一句話總結補強作用:

FPC局部區域為了焊接零件,增加補強以便安裝,補償其軟板厚度。

補強板,英文:stiffener,reinforcement,backing。

補強板材質一般可分為:FR4、PI、鋼片等;

FR4材質也可分為有鹵和無鹵材質,一般FPC采用沖壓成型,FR4邊緣易產生毛刺不良,部分改良產品可較好改善此不良。

PI補強一般用于金手指位補強,為了便于金手指插入連接器內部;

補強鋼片一般采用SUS304材質,此種材質具有以下兩個特點:

a.弱磁性,不會對磁性敏感產品如馬達等產生影響。

b.不銹性,表面光亮,不會氧化變色。

補強鋼片一般可分為:普通補強鋼片、鍍鎳補強鋼片;

普通補強鋼片用于一般產品,無補強接地要求的產品;

鍍鎳補強鋼片用于有接地要求的產品,鎳穩定性好,能夠保證較低的電阻值;

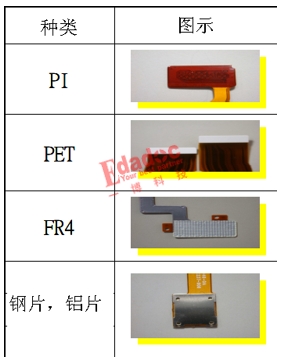

補強板的種類:

不銹鋼片(SS:Stainless Steel),客戶圖紙上標注是SUS,實際上這就是鋼片補強,SUS是鋼片的常用型號。

鋁片(AL:Aluminum)

FR4

聚酰亞胺(PI)Polyimide

聚酯(PET)Polyester

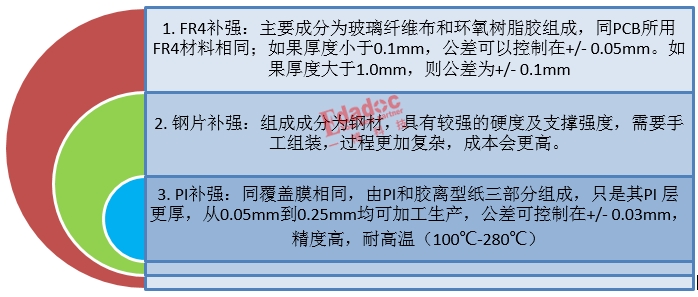

下圖是我們常用的補強類型,你能分清是哪一種嗎?

下面是常用的三種補強的生產復雜度的對比:

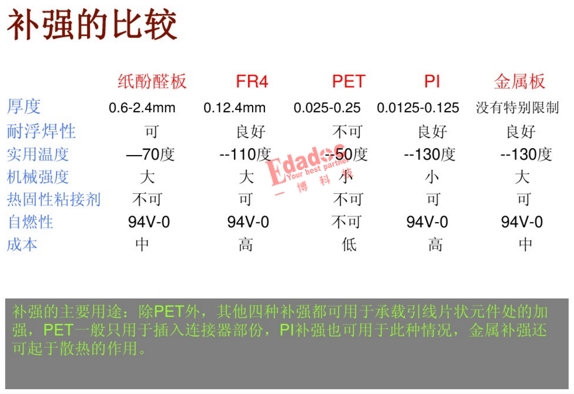

補強的選材:

PI 補強

適用于帶有拔插手指的插頭板。此類板必須使用 PI 補強,其他類型的板及除插頭位的其他位置建議不要采用 PI 補強,此材料強度不夠且價格也較高。

FR-4補強

FR-4補強使用于按鍵、側鍵類等大部分板,但此補強要用純膠壓合才能起到較好的補強作用。

鋼片補強

鋼片補強適用于帶連接器的多層板及單雙面板。此補強硬度比較高,生產出來的板比較平整,SMT 也比較好操作。建議帶連接器的各類板均可使用鋼片補強(需接地的補強需要特殊的補強)。

DFM案例:

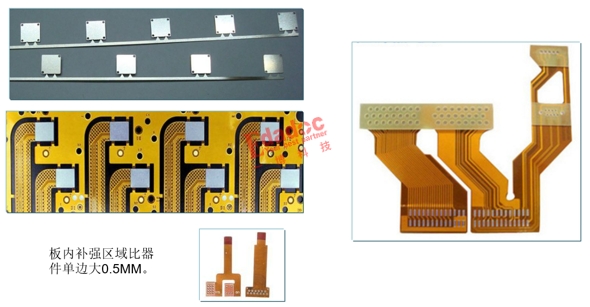

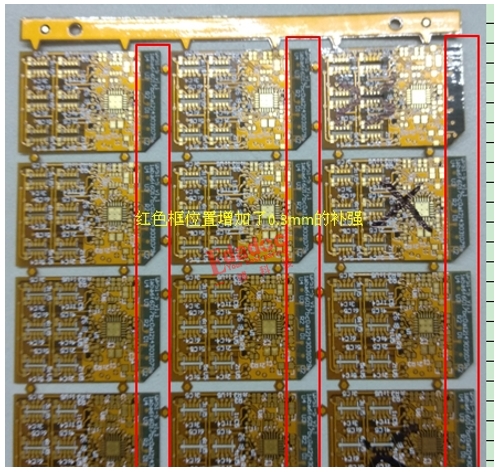

客戶設計的FPC板子雙面布局,板邊有連接器,客戶在PCB生產時要求加補強。工廠按照客戶的要求添加,FPC板子生產出來以后,急急忙忙送到了焊接廠。

于是世紀難題出現了。

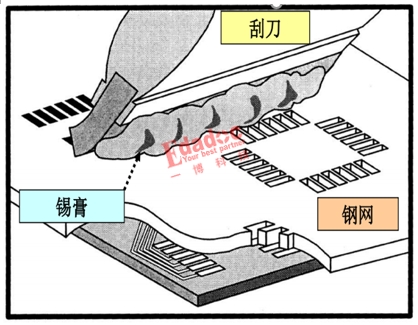

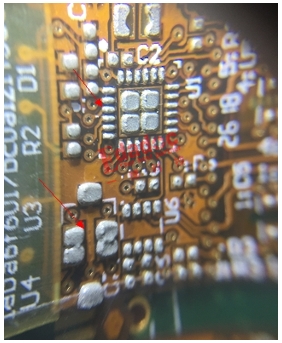

焊接廠收到板子后,工程在做DFA評估時,反饋TOP無法控制錫膏的正常厚度,不能生產。

正常的焊接工序是:先焊接器件少的一面BOTTOM面,再焊接器件多的一面TOP面。

TOP板邊有補強。并且增加了0.3mm的補強,相當于在PCB板表面多出了0.3mm的一個凸起部分。導致印刷時凸起部分周邊錫膏厚度無法控制。

經過工程和產線多次印刷驗證,板邊補強位置錫量太厚, 嚴重影響QFN 焊接。

導致過爐后QFN全部連錫。

現在物料已經全部到位,準備正常生產。請工程與客戶溝通,重新更換PCB板,取消補強位置。

木已成舟。只能讓客戶重新找制板廠想辦法把貼上的補強重新拆掉,滿足了焊接的需求。

聽完大師兄的講解,林如煙感對趙理工感嘆道,這真是生活給了你一記響亮的耳光。 趙理工說我趕緊把右臉也遞上。 林如煙白了趙理工一眼,嗔怪道:“瞧你那德行”。

本期問題:

關于FPC補強的設計,大家是否遇到相似的案例,最后是怎么解決的,大家一起聊起來。